Industrial Consultancy & Sponsored Research (IC&SR)

# Method and Electronic Device for mitigating Micro-Architectural sidechannel attack by Dynamic Resource Allocation **IITM Technology Available for Licensing**

### **Problem Statement**

Indian Institute of Technology Madras

· The problem statement discussed in the present invention is how to prevent the micro-architectural attacks the wherein system incur high overheads and other issues related to system performance issues & etc.

Hence, subject invention addresses the issue efficiently.

# Technology Category/Market

Technology:; Method & Electronic Device for Micro-Architectural side-channel mitigating attack:

Industry/Application: Computer Technology, Hardware, Software, & Algorithm, Servers, Cloud, Storage, Networking Devices, & etc.; Market: The global high performance computing market is projected to reach at a CAGR of 7.5% during the period (2024-30).

#### Technology

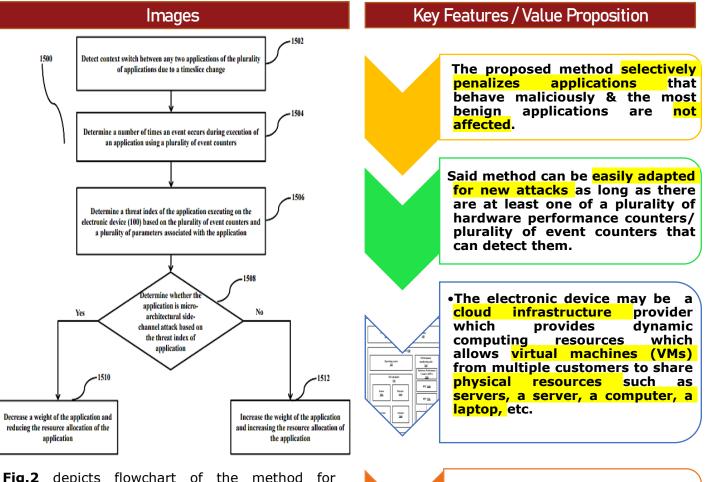

- □ Present patent describes a **method** & device that uses hardware performance counters to detect malicious tasks with micro-architectural attack-like behavior. (Refer Fig.1 & Fig.2)

- □ Upon detection, the proposed method provides a mechanism to degrade and malicious program threads upgrade based on their behavior.

- □ This significantly **reduces the impact** of the false-positives on benign applications, while detecting **malicious threads** with high accuracy using features implemented in the hardware.

- The method for mitigating microа architectural side-channel attack by dynamically allocating resources to a plurality applications by an electronic device, of comprising a few steps shown in Fig.2.

# Shared Hardware Attacker resource Information Leakage Victim Sensed runtime behavior Actuator Supervisor Control values to Detector reduce CPU share Proposed OS scheduler

Fig.1 depicts an overview of the method for the mitigating micro-architectural side-channel attack by dynamically allocating resources to the plurality of threads by an electronic device;

- The **electronic device** includes а communicator , a memory and a processor.

- Said communicator is configured to perform communications with the virtual machines (VMs) which share physical the resources of the electronic device.

## TRL (Technology Readiness Level)

TRL-4, Technology validated in Lab;

# Intellectual Property

#### IITM IDF Ref. 1998; Patent No.495535

#### Research Lab

**Prof. Chester Dominic Rebeiro,** Dept. of Computer Science & Engineering

**CONTACT US**

Dr. Dara Ajay, Head TTO Technology Transfer Office, IPM Cell- IC&SR, IIT Madras

**IITM TTO Website**: https://ipm.icsr.in/ipm/ Email: headtto-icsr@icsrpis.iitm.ac.in

tto-mktg@icsrpis.iitm.ac.in

Phone: +91-44-2257 9756/ 9719

# Indian Institute of Technology Madras

# Industrial Consultancy & Sponsored Research (IC&SR)

Fig.2 depicts flowchart of the method mitigating the micro-architectural side-channel attack by dynamically allocating resources to the plurality of applications;

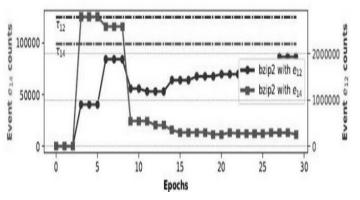

Fig.3 depicts timing diagram illustrating a benign thread breaching the threshold & being penalized for a brief period of time;

#### **CONTACT US**

Dr. Dara Ajay, Head TTO Technology Transfer Office, IPM Cell- IC&SR, IIT Madras

**IITM TTO Website:** https://ipm.icsr.in/ipm/

Email: smipm-icsr@icsrpis.iitm.ac.in sm-marketing@imail.iitm.ac.in Phone: +91-44-2257 9756/ 9719

Efficiently brings down the cost of

Once a benign thread which is

executes without any additional

the

flagged,

benian

the CPU share and

is

thread

a false penalization.

erroneously

unflagged,

overheads.

regains